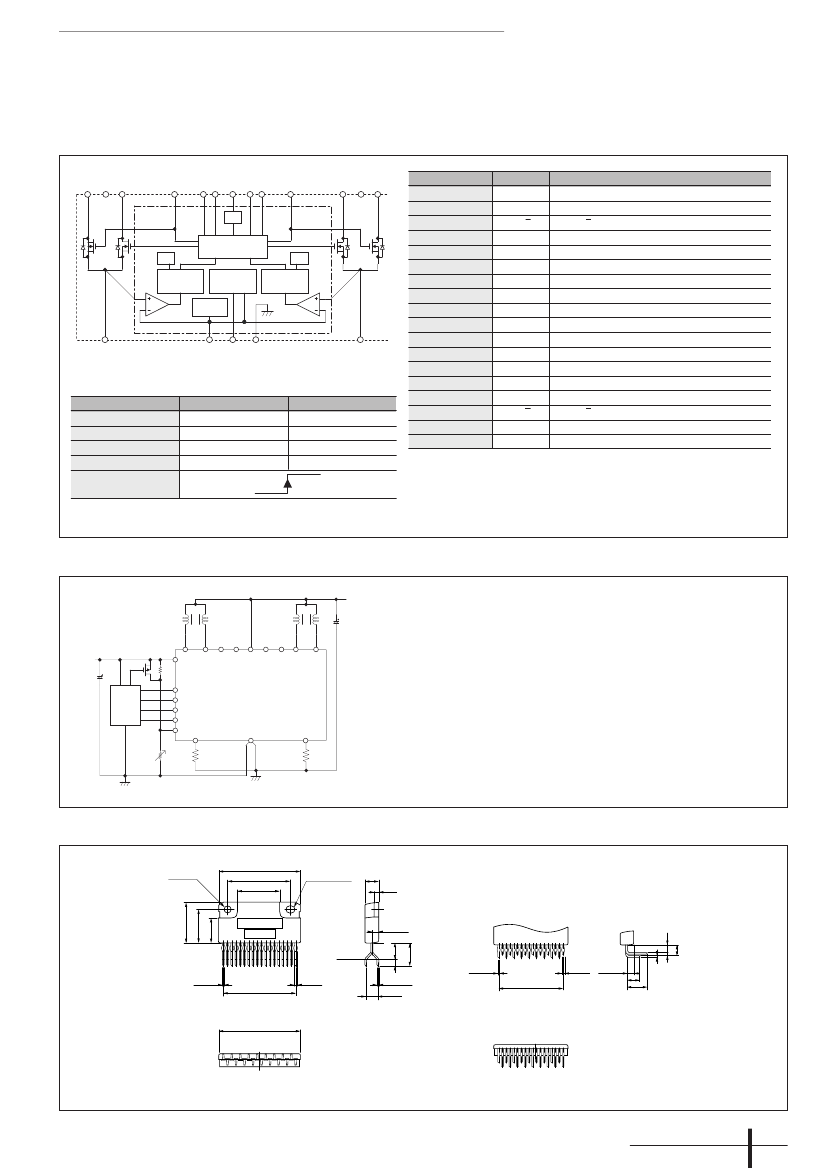

SLA7050M/SLA7051M/SLA7052M

sInternal

Block Diagram and Pin Assignment

CW/CCW

Full/Half

OutA/

OutB/

Clock

OutA

1

OutB

Pin No.

1

2

Symbol

OutA

NC

OutA

GA

V

CC

SenseA

Clock

Sync

Ref

GND

CW/CCW

Full/Half

SenseB

V

S

GB

OutB

NC

OutB

Phase A output

No Connection

Phase A output

No Connection

Logic supply

Phase A current sense

Step Clock input

Function

Vcc

GA

GB

Truth Table

L

CW/CCW

Full/Half

REF

Sync

Clock

CW

Full

Enable

Asynchronous

H

CCW

Half

Disable

Synchronous

* REF terminal turns into normal operation at VREF < 1.5V.

The output is disabled (Output OFF) at VREF > 2V.

sTypical

Connection Diagram

Vs=10~44V

CA

OutA/

OutB/

OutA

OutB

sExternal

Dimensions (ZIP18 with Fin [SLA18Pin])

φ

3.2

±0.15

31

±0.2

24.4

±0.2

16.4

±0.2

16

±0.2

13

±0.2

9.9

±0.2

6.7

±0.5

R-End

+0.2

0.65

–0.1

+0.2

1

–0.1

9.7

–0.5

+1

+0.2

0.55

–0.1

17×P1.68

±0.4

=28.56

±1

31.3

±0.2

4

±0.7

(3)

0.65

–0.1

1

–0.1

17×P1.68

±0.4

=28.56

±1

1 2 3

. . . . . . .

18

123

. . . . . . .

18

Forming No. No.871

Forming No. No.872

0.55

–0.1

1.6

±0.6

+0.2

+0.2

+0.2

2.2

±0.6

6

±0.6

7.5

±0.6

3

±0.6

Part Number

Lot No.

2.45

±0.2

4.6

±0.6

NC

2

6

SenseA

CB

NC

Vs

3

4

11 12

14

Reg

7

5

15

16

17

18

MIC

GA

3

GB

4

OSC

Sequencer

GA/

OSC

PWM

Control

Sleep

Circuit

Synchro

Control

GB/

5

6

PWM

Control

7

8

9

10

Synchronous PWM control signal input

Control current setting & output OFF

Device GND

Normal/reverse control input

Full/Half Step control input

Phase B current sense

Load supply (motor supply)

No Connection

Phase B output

No Connection

Phase B output

9

8

10

13

11

12

13

14

15

16

17

18

REF

NC

Sync

GA

GND

Vs

SenseB

1

Vcc=3.0~5.5V

Disable

Q1

7

Micro-

computer,

etc.

11

12

8

9

Clock

r1

5

Vcc

3

2

4

14

15

17

16 18

Rs=0.1 to 2Ω (Power dissipation should be: P..I

O2

×

R

S

)

=

R1=10kΩ

CA=100

µ

F/50V

R2=5.1kΩ (VR) CB=10

µ

F/10V

Q1:T.B.D

* V

CC

line noise precaution:

The device may malfunction if the V

CC

line noise exceeds 0.5V.

* Be sure to connect the unused logic input terminals (CW/CCW, F/H, Sync) to V

CC

or GND. If they are open, the device will malfunction.

* GND pattern precaution:

Separating the V

CC

system GND (S-GND) and V

S

system GND (P-GND) from the

device GND (10-Pin) helps to reduce noise.

CW/CCW

Full/Half

Sync

REF

6

SLA7050M

SLA7051M

SLA7052M

GB

NC

10

13

RsB

SenseA

GND

SenseB

r2

RsA

S-GND

P-GND

(Unit : mm)

φ

3.2

±0.15

×3.8

4.8

±0.2

1.7

±0.1

ICs

105